Poll

JTAGTest

JTAGTest is IEEE 1149.1 JTAG boundary scan debugging, testing and programming solution.

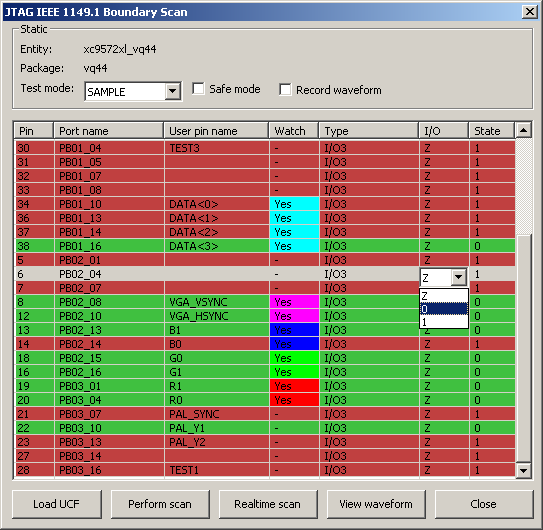

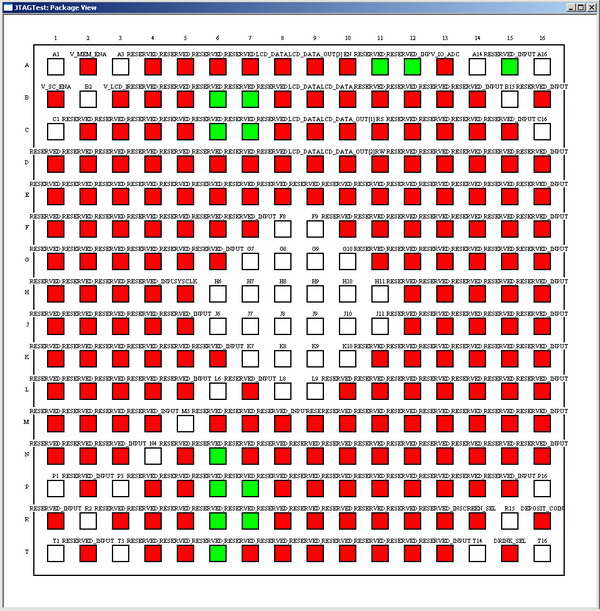

It's invaluable tool for all embedded designers, production houses and service companies. JTAGTest provides a significant aid for PCB debugging, prototyping, testing and repairing. Using an IEEE 1149.1 (JTAG) boundary-scan, device pin signals or internal signals can be monitored in real-time without interfering with the normal device operation and you can change pin state manually. The scan speed can be as high as allowed by your computer and the JTAG connection. Pin state view is provided in listing form or visual chip view:

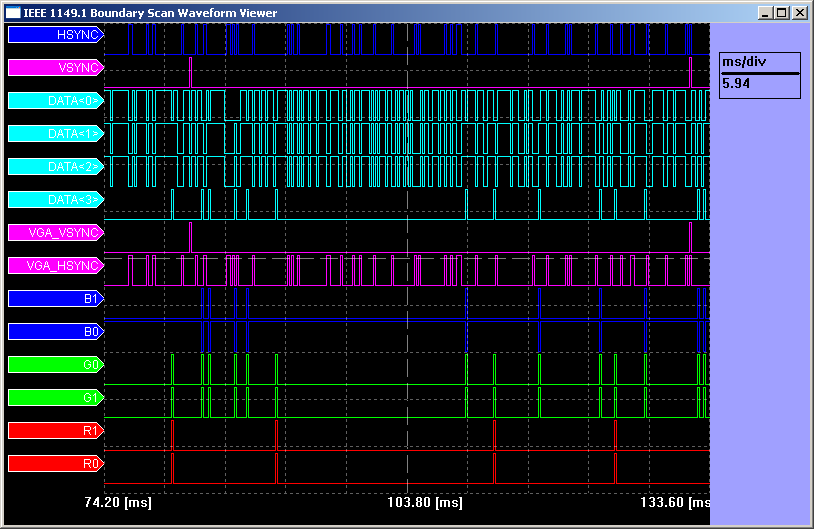

Alternatively data can be stored during realtime boundary scan in memory and then viewed as on logical analyzer. All this via 4 JTAG wires:

JTAGTest is multiplatform! Both Microsoft Windows and Linux/Unix are supported!

Key features

- JTAG IEEE 1149.1 and BSDL compliant

- Automatic JTAG Scan chain detection

- Easy to use interface

- Visualised boundary scan debugging

- Probing and controlling each pin via JTAG

- BSDL support

- Support for thousands of ICs

- SVF programming (CPLD/FPGA/MCU)

- SVF automated board testing

- Hardware supporting more than 20 JTAG pinouts

Requirements

- PC with Windows 2000/XP/Vista or Linux

- 256 MB RAM

- 1GB HDD space (for BSDL files)

- USB 2.0 port

- Will not want to choose the original firm the time you needing cash advance

- Less than perfect credit does not you can not receive a money advance

- Distribute your trusty finances due to visit to repay the student loan

- Est-ce nécessaire près octroyer l'accès fondés légers à manifestes jeux parmi raie

- Pourquoi les jeux selon barre auprès les infimes doivent être retour que