# DPA Circuitry and rx\_dpa\_locked Signal Behavior in Stratix III Devices

### Introduction

The receiver PLL provides eight clock phases to the DPA circuitry. The eight clock phases are separated by 45° and at a frequency equal to the serial data rate. After power up or reset, the DPA circuitry selects an optimum clock phase out of these eight clock phases to sample the received data. The DPA circuitry does not require a fixed training pattern to select the optimum phase. After power up or reset, the DPA circuitry relies on transitions on the received data to select the optimum phase.

## **ALTLVDS Megafunction**

The ALTLVDS megafunction provides an optional output signal rx\_dpa\_locked to indicate when the DPA has locked to the optimum phase. In Stratix<sup>®</sup> III devices, the logic that drives the rx\_dpa\_locked signal is implemented in the FPGA fabric and is automatically instantiated on a per-channel basis along with the ALTLVDS instance. Once the DPA locks to the optimum phase, the rx\_dpa\_locked signal always stays high until you assert the rx\_reset signal of the associated LVDS channel or the pll\_areset signal of the receiver PLL providing the eight clock phases to the DPA circuitry.

The rx\_dpa\_locked signal is no longer driven by the hard macro in Stratix III devices. The rx\_dpa\_locked signal only indicates an initial DPA lock condition to the optimum phase after power up or reset. The rx\_dpa\_locked signal does not get de-asserted if the DPA selects a new phase out of the eight clock phases to sample the received data. You must not use the rx\_dpa\_locked signal to determine a DPA Loss of Lock condition.

Altera recommends:

- Resetting the synchronizer (FIFO buffer) using the rx\_fifo\_reset signal once after the rx\_dpa\_locked signal gets asserted and before valid data is received.

- Using error checkers; for example, Cyclic Redundancy Check (CRC) or Diagonal Interleaved Parity (DIP-4), to validate the integrity of the LVDS link.

#### Configuring the ALTLVDS Megafunction in DPA Mode

The receiver ALTLVDS MegaWizard<sup>®</sup> Plug-In Manager provides a **Use External PLL** option to allow more flexible settings for the receiver PLL. If this option is disabled, the receiver PLL is automatically instantiated as a part of ALTLVDS instance. If this option is enabled, you must use the ALTPLL MegaWizard Plug-In Manager to instantiate the receiver PLL for the LVDS link.

The behavior of the rx\_dpa\_locked signal is same with or without the Use External PLL option enabled.

The logic that drives the rx\_dpa\_locked signal needs inputs from the receiver PLL and the LVDS receiver channel. If the **Use External PLL** option is disabled, the ALTLVDS instance automatically provides the necessary inputs from the receiver PLL and the LVDS receiver channel to this logic. If the **Use External PLL** option is enabled, you must make the following connections between the ALTPLL and ALTLVDS instances in your design.

| Table 1. Signal Interface Between ALTPLL and ALTLVDS |                                                |

|------------------------------------------------------|------------------------------------------------|

| From ALTPLL (Note 1)                                 | To ALTLVDS Receiver                            |

| Serial clock output (c0)                             | rx_inclock (serial clock input)                |

| Load enable output (c1)                              | $rx_enable$ (load enable for the deserializer) |

| Parallel clock output (c2)                           | rx_syncclock (parallel clock input)            |

| ~(locked)                                            | pll_areset (asynchronous PLL reset port)       |

Note to Table 1:

The table shows the serial clock output, load enable output, and parallel clock output generated on ports c0, c1, and c2 of the ALTPLL instance as an example. You can choose any of the PLL output clock ports to generate the above three interface clocks.

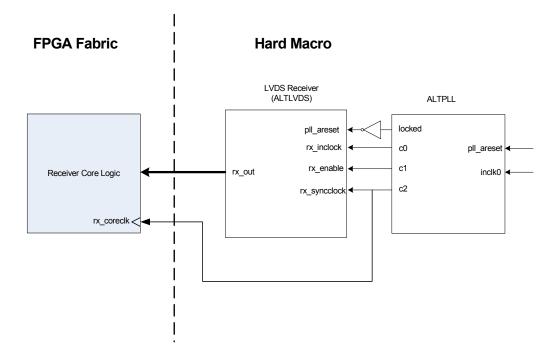

Figure 1 illustrates the required ALTPLL-to-ALTLVDS port connections when the ALTLVDS receiver instance is configured in DPA mode with the **Use External PLL** option enabled.

The two input ports, rx\_inclock and rx\_enable, to the LVDS receiver instance are available through the ALTLVDS MegaWizard Plug-In Manager. The ports pll\_areset and rx\_syncclock are not available through the ALTLVDS MegaWizard Plug-In Manager and must be manually included by modifying the .v or .vhd wrapper file generated by the ALTLVDS MegaWizard Plug-In Manager.

#### **Altera Corporation**

Instantiation of rx\_syncclock in the ALTLVDS wrapper file is mandatory. The Quartus II compiler errors out if this port is not instantiated and connected as shown in Figure 1.

The following example illustrates required modifications to the verilog wrapper file generated by the ALTLVDS MegaWizard Plug-In Manager configured in DPA mode with the **Use External PLL** option selected:

*Example of modified verilog wrapper file (required modifications in green text)*

```

module receiver_io (

rx enable,

rx<sup>-</sup>in,

rx inclock,

rx_reset,

rx dpa locked,

rx out.

rx syncclock, // parallel clock input from ALTPLL

pll areset); // inverse of locked signal from ALTPLL

input

rx enable:

input

[0:\overline{0}] rx in;

rx inclock;

input

input

[0:0] rx reset;

input [0:0] pll areset; // declaration of pll areset port

input [0:0] rx_syncclock; // declaration of rx_syncclock port

[0:0] rx dpa locked;

output

[3:0] rx out;

output

wire [3:0] sub wire0;

wire [0:0] sub wire1;

wire [3:0] rx out = sub wire0[3:0];

wire [0:0] rx dpa locked = sub wire1[0:0];

altlvds rx altlvds rx component (

.rx inclock (rx inclock),

.rx reset (rx reset),

.rx_in (rx_in),

.rx enable (rx enable),

.rx out (sub wire0),

.rx dpa locked (sub wire1),

.pll_areset (pll_areset), // instantiation of pll_areset port

.rx cda max (),

.rx cda reset (1'b0),

.rx_channel_data_align (1'b0),

.rx_coreclk (1'b1),

.rx_data_align (1'b0),

.rx data align reset (1'b0),

.rx deskew (1'b0),

.rx divfwdclk (),

.rx dpll enable (1'b1),

.rx dpll hold (1'b0).

.rx dpll reset (1'b0),

.rx fifo reset (1'b0),

.rx locked (),

.rx outclock (),

.rx_pll_enable (1'b1),

.rx readclock (1'b0),

.rx_syncclock (rx_syncclock)); // instantiation of rx_syncclock port

```

The following example illustrates the required ALTPLL-to-ALTLVDS connections in designs with ALTLVDS configured in DPA mode with the **Use External PLL** option selected:

| module   | top(                                         |

|----------|----------------------------------------------|

|          | top_pll_areset,                              |

|          | top_rx_refclk,                               |

|          | top_rx_reset,                                |

|          | top_rx_in                                    |

|          | );                                           |

| input    | top_pll_areset;                              |

| input    | top_rx_refclk;                               |

| input    | top_rx_reset;                                |

| input    | top_rx_in;                                   |

| wire ser | rial_clk_pll_to_lvds;                        |

|          | ud_enable_pll_to_lvds;                       |

|          | rallel_clk_pll_to_lvds;                      |

| wire rx_ | pll_locked_pll_to_lvds;                      |

| //ALTPI  | LL receiver PLL instantiation                |

| pll rx   | pll rx inst                                  |

|          | (.areset(top_pll_areset),                    |

|          | .inclk0(top_rx_refclk),                      |

|          | .c0(serial_clk_pll_to_lvds),                 |

|          | .c1(load_enable_pll_to_lvds),                |

|          | .c2(parallel_clk_pll_to_lvds),               |

|          | .locked(rx_pll_locked_pll_to_lvds)           |

|          | );                                           |

| //ALTLV  | VDS receiver channel instantiation           |

| receiver | r io receiver io inst                        |

|          | ( <i>rx</i> enable(load enable pll to lvds), |

|          | .rx inclock(serial clk pll to lvds),         |

|          | rx in(top rx in),                            |

|          | .rx_reset(top_rx_reset),                     |

|          | .rx_syncclock(parallel_clk_pll_to_lvds),     |

|          | .rx_out(lvds_rx_out),                        |

|          |                                              |

|          | .pll areset(~(rx pll locked pll to lvds))    |

endmodule

101 Innovation Drive San Jose, CA 95134 www.altera.com Copyright © 2008 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and toher countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.